- 您现在的位置:买卖IC网 > Sheet目录3890 > PIC16F74T-E/L (Microchip Technology)IC MCU FLASH 4KX14 A/D 44PLCC

Micrel, Inc.

KSZ8851-16MLLJ

March 2010

67

M9999-030210-1.0

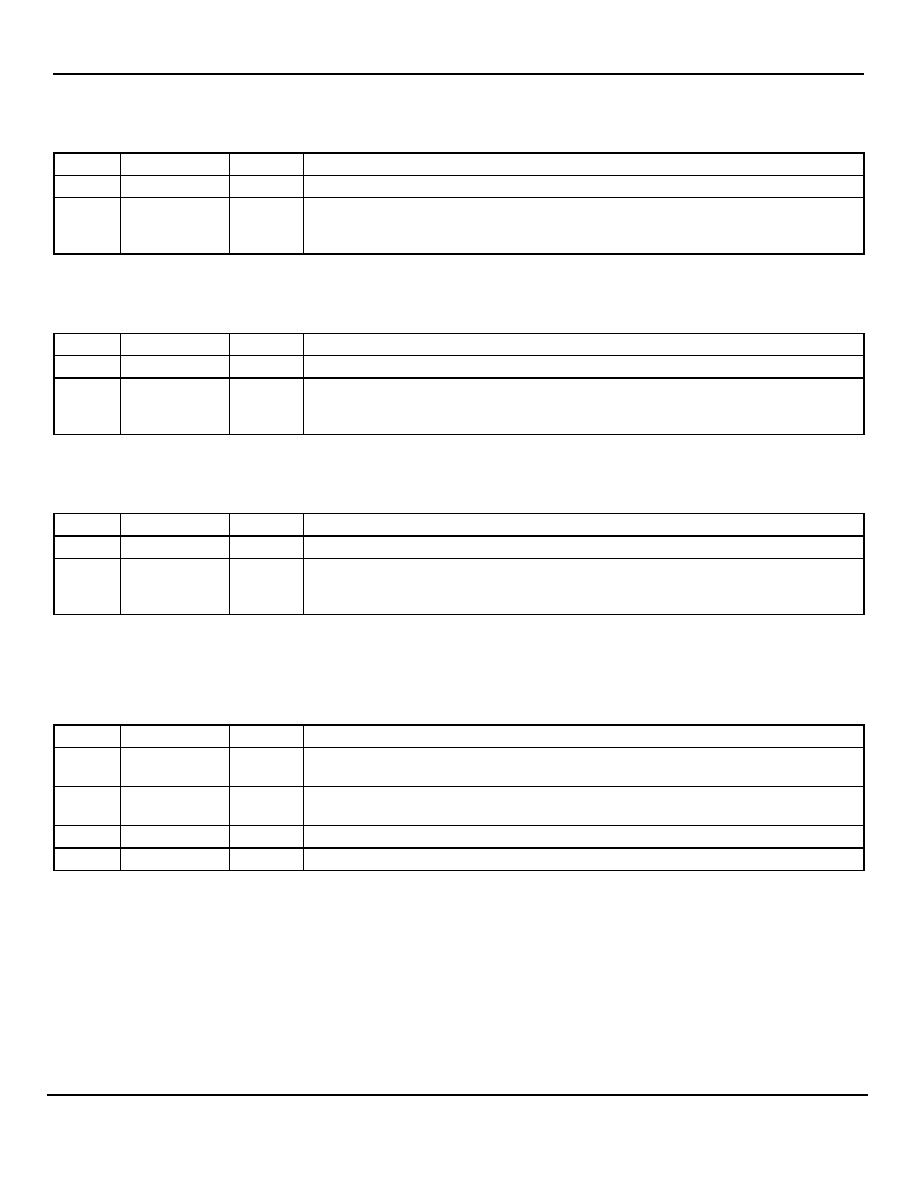

Flow Control Low Watermark Register (0xB0 – 0xB1): FCLWR

This register is used to control the flow control for low watermark in QMU RX queue.

Bit

Default Value

R/W

Description

15-12

-

RW

Reserved

11-0

0x0500

RW

FCLWC Flow Control Low Watermark Configuration

These bits are used to define the QMU RX queue low watermark configuration. It is in

double words count and default is 5.12 KByte available buffer space out of 12 KByte.

Flow Control High Watermark Register (0xB2 – 0xB3): FCHWR

This register is used to control the flow control for high watermark in QMU RX queue.

Bit

Default Value

R/W

Description

15-12

-

RW

Reserved

11-0

0x0300

RW

FCHWC Flow Control High Watermark Configuration

These bits are used to define the QMU RX queue high watermark configuration. It is in

double words count and default is 3.072 K Byte available buffer space out of 12 KByte.

Flow Control Overrun Watermark Register (0xB4 – 0xB5): FCOWR

This register is used to control the flow control for overrun watermark in QMU RX queue

Bit

Default Value

R/W

Description

15-12

-

RW

Reserved

11-0

0x0040

RW

FCLWC Flow Control Overrun Watermark Configuration

These bits are used to define the QMU RX queue overrun watermark configuration. It is in

double words count and default is 256 Bytes available buffer space out of 12 Kbyte.

0xB6 – 0xBF: Reserved

Chip ID and Enable Register (0xC0 – 0xC1): CIDER

This register contains the chip ID and the chip enable bit.

Bit

Default

R/W

Description

15-8

0x88

RO

Family ID

Chip family ID

7-4

0x7

RO

Chip ID

0x7 is assigned to KSZ8851-16MLLJ

3-1

0x1

RO

Revision ID

0

0x0

RW

Reserved

0xC2 – 0xC5: Reserved

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16C765T-I/L

IC MCU OTP 8KX14 USB 44PLCC

PIC18C442T-E/L

IC MCU OTP 8KX16 A/D 44PLCC

PIC16C621A-40/SS

IC MCU OTP 1KX14 COMP 20SSOP

PIC16C622A-40/SS

IC MCU OTP 2KX14 COMP 20SSOP

PIC16CE623-30/SO

IC MCU OTP 512X14 EE COMP 18SOIC

PIC16CE624-30/SO

IC MCU OTP 1KX14 EE COMP 18SOIC

PIC16CE624-30/SS

IC MCU OTP 1KX14 EE COMP 20SSOP

PIC16CE623-30/SS

IC MCU OTP 512X14 EE COMP 20SSOP

相关代理商/技术参数

PIC16F74T-E/ML

功能描述:8位微控制器 -MCU 7KB 192 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F74T-E/PT

功能描述:8位微控制器 -MCU 7KB 192 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F74T-I/L

功能描述:8位微控制器 -MCU 7KB 192 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F74T-I/ML

功能描述:8位微控制器 -MCU 7KB 192 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F74T-I/PT

功能描述:8位微控制器 -MCU 7KB 192 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F74T-I/PT152

制造商:Microchip Technology Inc 功能描述:

PIC16F74T-I/PTG

功能描述:8位微控制器 -MCU 7KB 192 RAM 33 I/O Lead Free Package RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F753-E/ML

制造商:Microchip Technology Inc 功能描述:3.5KB FLASH, 128 RAM, 8MHZ INT. OSC, 9-BIT DAC - Rail/Tube 制造商:Microchip Technology Inc 功能描述:IC PIC MCU 2K FLASH 16QFN 制造商:Microchip Technology Inc 功能描述:8-bit Microcontrollers - MCU 35KB Flsh 128 R 8MHz Int Osc 9-bit DAC